Microcontrollers - 8051 Architecture

8051 microcontroller is designed by Intel in 1981. It is an 8-bit microcontroller. It is built with 40 pins DIP (dual inline package), 4kb of ROM storage and 128 bytes of RAM storage, 2 16-bit timers. It consists of are four parallel 8-bit ports, which are programmable as well as addressable as per the requirement. An on-chip crystal oscillator is integrated in the microcontroller having crystal frequency of 12 MHz.

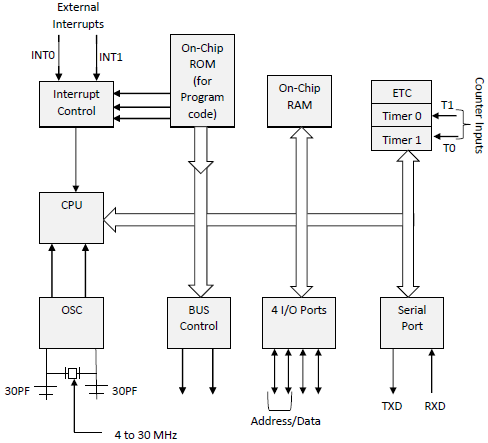

Let us now discuss the architecture of 8051 Microcontroller.

In the following diagram, the system bus connects all the support devices to the CPU. The system bus consists of an 8-bit data bus, a 16-bit address bus and bus control signals. All other devices like program memory, ports, data memory, serial interface, interrupt control, timers, and the CPU are all interfaced together through the system bus.

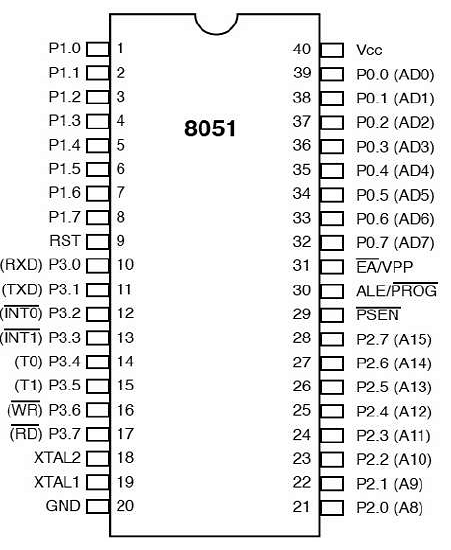

Microcontrollers - 8051 Pin Description

The pin diagram of 8051 microcontroller looks as follows −

- Pins 1 to 8 − These pins are known as Port 1. This port doesn’t serve any other functions. It is internally pulled up, bi-directional I/O port.

- Pin 9 − It is a RESET pin, which is used to reset the microcontroller to its initial values.

- Pins 10 to 17 − These pins are known as Port 3. This port serves some functions like interrupts, timer input, control signals, serial communication signals RxD and TxD, etc.

- Pins 18 & 19 − These pins are used for interfacing an external crystal to get the system clock.

- Pin 20 − This pin provides the power supply to the circuit.

- Pins 21 to 28 − These pins are known as Port 2. It serves as I/O port. Higher order address bus signals are also multiplexed using this port.

- Pin 29 − This is PSEN pin which stands for Program Store Enable. It is used to read a signal from the external program memory.

- Pin 30 − This is EA pin which stands for External Access input. It is used to enable/disable the external memory interfacing.

- Pin 31 − This is ALE pin which stands for Address Latch Enable. It is used to demultiplex the address-data signal of port.

- Pins 32 to 39 − These pins are known as Port 0. It serves as I/O port. Lower order address and data bus signals are multiplexed using this port.

- Pin 40 − This pin is used to provide power supply to the circuit.

Microcontrollers 8051 Input Output Ports

- 8051 microcontrollers have 4 I/O ports each of 8-bit, which can be configured as input or output. Hence, total 32 input/output pins allow the microcontroller to be connected with the peripheral devices.

- Pin configuration, i.e. the pin can be configured as 1 for input and 0 for output as per the logic state.

- Input/Output (I/O) pin − All the circuits within the microcontroller must be connected to one of its pins except P0 port because it does not have pull-up resistors built-in.

- Input pin − Logic 1 is applied to a bit of the P register. The output FE transistor is turned off and the other pin remains connected to the power supply voltage over a pull-up resistor of high resistance.

- Port 0 − The P0 (zero) port is characterized by two functions −

- When the external memory is used then the lower address byte (addresses A0A7) is applied on it, else all bits of this port are configured as input/output.

- When P0 port is configured as an output then other ports consisting of pins with built-in pull-up resistor connected by its end to 5V power supply, the pins of this port have this resistor left out.

Input Configuration

If any pin of this port is configured as an input, then it acts as if it “floats”, i.e. the input has unlimited input resistance and in-determined potential.Output Configuration

When the pin is configured as an output, then it acts as an “open drain”. By applying logic 0 to a port bit, the appropriate pin will be connected to ground (0V), and applying logic 1, the external output will keep on “floating”.In order to apply logic 1 (5V) on this output pin, it is necessary to build an external pullup resistor.Port 1

P1 is a true I/O port as it doesn’t have any alternative functions as in P0, but this port can be configured as general I/O only. It has a built-in pull-up resistor and is completely compatible with TTL circuits.Port 2

P2 is similar to P0 when the external memory is used. Pins of this port occupy addresses intended for the external memory chip. This port can be used for higher address byte with addresses A8-A15. When no memory is added then this port can be used as a general input/output port similar to Port 1.Port 3

In this port, functions are similar to other ports except that the logic 1 must be applied to appropriate bit of the P3 register.Pins Current Limitations

- When pins are configured as an output (i.e. logic 0), then the single port pins can receive a current of 10mA.

- When these pins are configured as inputs (i.e. logic 1), then built-in pull-up resistors provide very weak current, but can activate up to 4 TTL inputs of LS series.

- If all 8 bits of a port are active, then the total current must be limited to 15mA (port P0: 26mA).

- If all ports (32 bits) are active, then the total maximum current must be limited to 71mA.

- Microcontrollers - 8051 Interrupts

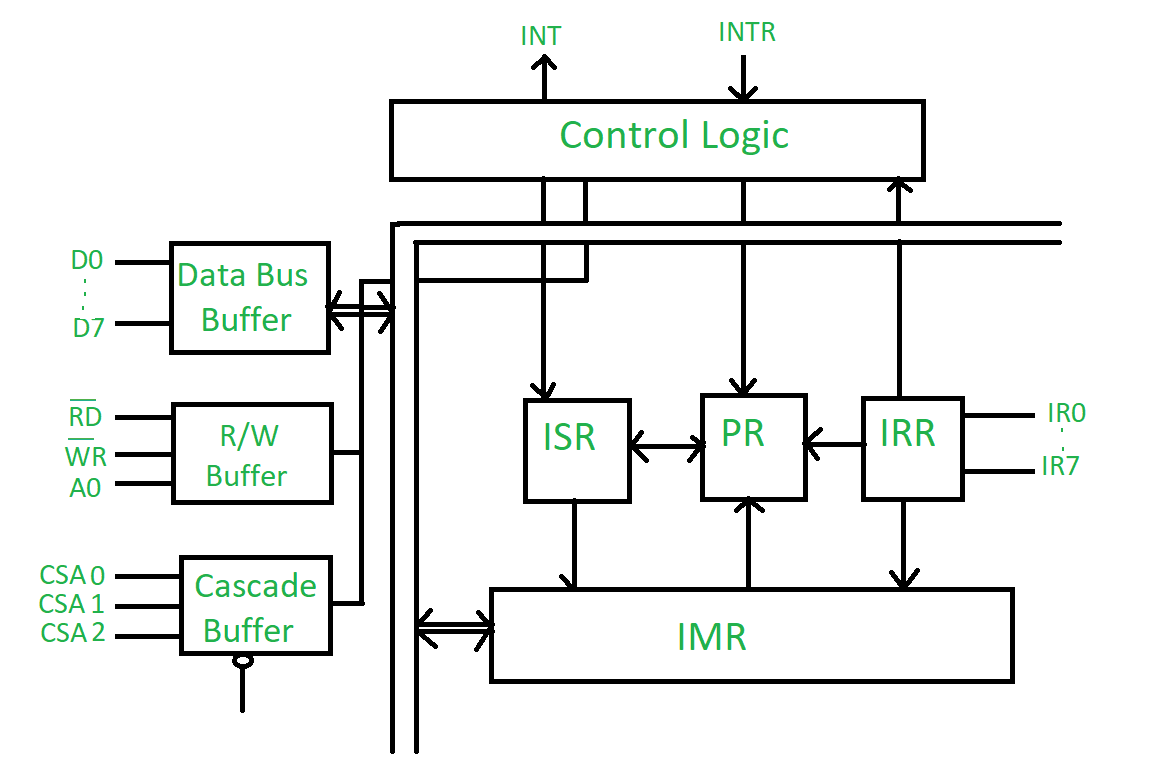

- Interrupts are the events that temporarily suspend the main program, pass the control to the external sources and execute their task. It then passes the control to the main program where it had left off.8051 has 5 interrupt signals, i.e. INT0, TFO, INT1, TF1, RI/TI. Each interrupt can be enabled or disabled by setting bits of the IE register and the whole interrupt system can be disabled by clearing the EA bit of the same register.

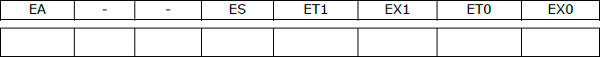

IE (Interrupt Enable) Register

This register is responsible for enabling and disabling the interrupt. EA register is set to one for enabling interrupts and set to 0 for disabling the interrupts. Its bit sequence and their meanings are shown in the following figure.

EA IE.7 It disables all interrupts. When EA = 0 no interrupt will be acknowledged and EA = 1 enables the interrupt individually. - IE.6 Reserved for future use. - IE.5 Reserved for future use. ES IE.4 Enables/disables serial port interrupt. ET1 IE.3 Enables/disables timer1 overflow interrupt. EX1 IE.2 Enables/disables external interrupt1. ET0 IE.1 Enables/disables timer0 overflow interrupt. EX0 IE.0 Enables/disables external interrupt0. IP (Interrupt Priority) Register

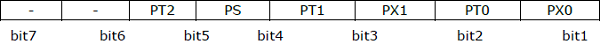

We can change the priority levels of the interrupts by changing the corresponding bit in the Interrupt Priority (IP) register as shown in the following figure.- A low priority interrupt can only be interrupted by the high priority interrupt, but not interrupted by another low priority interrupt.

- If two interrupts of different priority levels are received simultaneously, the request of higher priority level is served.

- If the requests of the same priority levels are received simultaneously, then the internal polling sequence determines which request is to be serviced.

- IP.6 Reserved for future use. - IP.5 Reserved for future use. PS IP.4 It defines the serial port interrupt priority level. PT1 IP.3 It defines the timer interrupt of 1 priority. PX1 IP.2 It defines the external interrupt priority level. PT0 IP.1 It defines the timer0 interrupt priority level. PX0 IP.0 It defines the external interrupt of 0 priority level. TCON Register

TCON register specifies the type of external interrupt to the microcontroller.